Help

Why you need a lab assistant when you breadboard

Wiring your first physical breadboard is a frustrating experience. One wrong connection and the circuit does not work. Without an experienced lab or teaching assistant by your side, it is difficult to find out where is the mistake. Our breadboard simulator acts as a virtual and patient lab assistant who checks your every connection to help you gain experience and confidence to breadboard correctly.

Practice does not make perfect. Only perfect practice makes perfect - Vince Lombardi

verified_user Complete wiring one circuit in this breadboard simulator and earn a digital badge. You need to sign in with your Google account first.

To complete wiring the breadboard

- Operate the switches in the circuit simulator. Read the description of the circuit for more information. The default circuit is the 1 to 2 demultiplexer. It is an easy circuit to understand and to breadboard.

- Using the circuit schematic, wire up the circuit in the breadboard simulator. When a wire end is placed in a socket of the breadboard that corresponds to a node on the schematic, the respective node of the schematic will turn red.

- If a correct connection is made, the wire ends will snap into the socket.

- When all the nodes are wired up, a red LED will light up near the VCC/GND terminals to indicate that the breadboard wiring is completed correctly.

- You may now operate the switches of the breadboard and observe the LED results.

Notes

- Click Help on menu to hide/show this Help panel. This site is optimised for computer browsers.

- All the VCC (red wire) and GND (black wire) connections are already done. When you wire up the actual circuit using the low cost Home Laboratory Kit, do remember to connect the VCC and GND wires.

- When you select a different schematic, the ones where you have completed the breadboard will be shown with a green background.

- The holes in the breadboard connected in blue are electrically connected.

- If you are unfamiliar with the breadboard, there are many resources available online that explains how they work. We recommend this quick Breadboard Infographic from Make Breadboarding Workshop or the longer Breadboard Tutorial from Science Buddies.

- Read Stony Brook University's paper that reports how their "virtual breadboard helped students to prepare for their labs, and significantly reduced the amount of time teaching assistants had to spend helping students in the actual lab."

Breadboard Simulator

Circuit Schematic & Simulator

1 to 2 demultiplexer

A 1 to 2 demultiplexer uses 1 select line (SW0) to determine which one of the 2 outputs (D0, D1) to route the input (SW1).

For more info, see demultiplexers

- Next steps

- Learn how to design a 1 to 2 Demultiplexer to obtain the above schematic.

- Wire up the actual circuit using the low cost Home Laboratory Kit and compare the results.

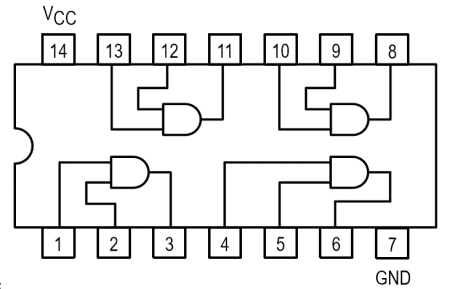

7408 Quad 2 Input AND Gate IC Pin Out

7404 NOT Gate IC Pin Out